# **Concurrent Computing**

Rachid Guerraoui

Petr Kuznetsov

January 6, 2017

# **Contents**

| 1. | Intro | oduction                                    | 9  |

|----|-------|---------------------------------------------|----|

|    | 1.1.  | A broad picture: the concurrency revolution | 9  |

|    | 1.2.  | The topic: shared objects                   | C  |

|    | 1.3.  | Linearizability                             | 1  |

|    | 1.4.  | Progress                                    | 2  |

|    | 1.5.  | Combining linearizability and wait-freedom  | 2  |

|    | 1.6.  | Object implementations                      | 3  |

|    | 1.7.  | Reducibility                                | 4  |

|    | 1.8.  | Organization                                | 4  |

|    | 1.9.  | Bibliographical notes                       | 5  |

| I. | Co    | rrectness 1                                 | 7  |

| 2. | Line  | earizability 1                              |    |

|    | 2.1.  | Introduction                                |    |

|    | 2.2.  | The Players                                 |    |

|    |       | 2.2.1. Processes                            |    |

|    |       | 2.2.2. Objects                              |    |

|    |       | 2.2.3. Histories                            |    |

|    |       | 2.2.4. Sequential histories                 |    |

|    |       | 2.2.5. Legal histories                      |    |

|    | 2.3.  | Linearizability                             |    |

|    |       | 2.3.1. The case of complete histories       |    |

|    |       | 2.3.2. The case of incomplete histories     |    |

|    |       | 2.3.3. Completing a linearizable history    |    |

|    | 2.4.  | Composition                                 |    |

|    | 2.5.  | Safety                                      |    |

|    | 2.6.  | Summary                                     |    |

|    | 2.7.  | Bibliographic notes                         | .2 |

| 3. |       | gress 3                                     |    |

|    |       | Introduction                                |    |

|    | 3.2.  | Implementation                              |    |

|    |       | 3.2.1. High-level and low-level objects     |    |

|    |       | 3.2.2. Zooming into histories               |    |

|    | 3.3.  | Progress properties                         |    |

|    |       | 3.3.1. Variations                           |    |

|    |       | 3.3.2. Bounded termination                  |    |

|    |       | 3.3.3. Liveness                             |    |

|    | 3.4.  | Linearizability and wait-freedom            |    |

|    |       | 3.4.1. A simple example                     | 7  |

|     |                   | 3.4.2. A more sophisticated example                                   | 39 |

|-----|-------------------|-----------------------------------------------------------------------|----|

|     | 3.5.              | Summary                                                               | 40 |

| II. | C+/               | orago objects                                                         | 43 |

|     | Sil               | orage objects                                                         | 43 |

| 4.  | Sim               | ple register transformations                                          | 45 |

|     | 4.1.              | Definitions                                                           | 45 |

|     | 4.2.              | Proving register properties                                           | 46 |

|     | 4.3.              | Register transformations                                              | 48 |

|     | 4.4.              | Two simple transformations                                            | 49 |

|     |                   | 4.4.1. Safe/regular registers: from single reader to multiple readers | 49 |

|     |                   | 4.4.2. Binary multi-reader registers: from safe to regular            | 50 |

|     | 4.5.              | From binary to $b$ -valued registers                                  | 51 |

|     |                   | 4.5.1. From safe bits to safe <i>b</i> -valued registers              | 51 |

|     |                   | 4.5.2. From regular bits to regular b-valued registers                | 52 |

|     |                   | 4.5.3. From atomic bits to atomic b-valued registers                  | 54 |

|     | 4.6.              | Bibliographic notes                                                   | 56 |

| 5.  | Tim               | estamp-based register transformations                                 | 57 |

|     | 5.1.              | •                                                                     | 57 |

|     | 5.2.              |                                                                       |    |

|     | 5.3.              | -                                                                     |    |

|     |                   | Concluding remark                                                     |    |

|     |                   | Bibliographic notes                                                   |    |

| 6.  | Opti              | imal atomic bit construction                                          | 63 |

| -   | •                 | Introduction                                                          |    |

|     |                   | Lower bound                                                           |    |

|     |                   | 6.2.1. Digests and sequences of writes                                |    |

|     |                   | 6.2.2. Impossibility result and lower bound                           |    |

|     | 6.3.              | From three safe bits to an atomic bit                                 |    |

|     |                   | 6.3.1. Base architecture of the construction                          |    |

|     |                   | 6.3.2. Handshaking mechanism and the write operation                  |    |

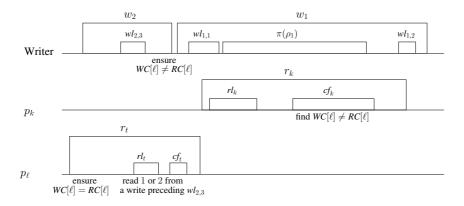

|     |                   | 6.3.3. An incremental construction of the read operation              |    |

|     |                   | 6.3.4. Proof of the construction                                      |    |

|     |                   |                                                                       | 74 |

|     | 6.4.              | Bibliographic notes                                                   |    |

| 7   | Δtοι              | mic multivalued register construction                                 | 75 |

| • • | 7.1.              | From single-reader regular to multi-reader atomic                     | 75 |

|     | 7.1.              |                                                                       | 75 |

|     | 7.2.              | The algorithm                                                         |    |

|     |                   | Bibliographic notes                                                   | 81 |

|     | , . <del> -</del> | 1411/11/15/11/11/11/11/11/11/11/11/11/11/1                            |    |

| III. | Sn    | apshot objects                                               | 83  |

|------|-------|--------------------------------------------------------------|-----|

| 8.   | Coll  | ects and snapshots                                           | 85  |

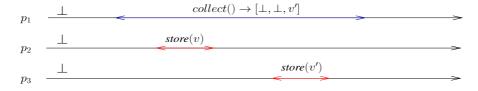

|      | 8.1.  | Collect object                                               | 85  |

|      |       | 8.1.1. Definition and implementation                         | 85  |

|      |       | 8.1.2. A collect object has no sequential specification      | 86  |

|      | 8.2.  | Snapshot object                                              | 87  |

|      |       | 8.2.1. Definition                                            | 87  |

|      |       | 8.2.2. The sequential specification of snapshot              | 87  |

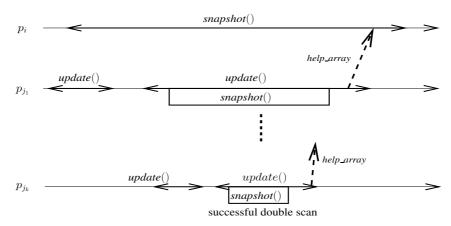

|      |       | 8.2.3. Non-blocking snapshot                                 | 88  |

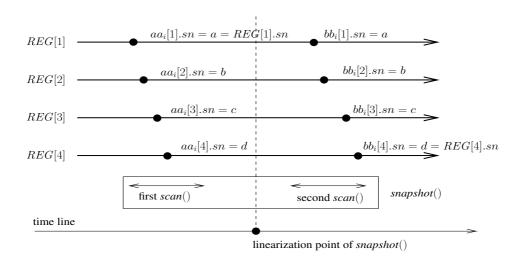

|      |       | 8.2.4. Wait-free snapshot                                    | 91  |

|      |       | 8.2.5. The snapshot object construction is bounded wait-free | 92  |

|      |       | 8.2.6. The snapshot object construction is atomic            | 93  |

|      | 8.3.  | Bounded atomic snapshot                                      | 94  |

|      |       | 8.3.1. Double collect and helping                            | 94  |

|      |       | 8.3.2. Binary handshaking                                    | 95  |

|      |       | 8.3.3. Bounded snapshot using handshaking                    | 95  |

|      |       | 8.3.4. Correctness                                           | 95  |

|      | 8.4.  | Bibliographic notes                                          | 97  |

|      |       |                                                              |     |

| 9.   | lmm   | nediate snapshot and iterated immediate snapshot             | 99  |

|      | 9.1.  | Immediate snapshot object                                    | 99  |

|      |       | 9.1.1. Definition                                            | 99  |

|      |       | 9.1.2. A one-shot immediate snapshot construction            | 99  |

|      |       | 9.1.3. A participating set algorithm                         | 100 |

|      | 9.2.  | A connection between (one-shot) renaming and snapshot        | 102 |

|      |       | 9.2.1. A weakened version of the immediate snapshot problem  | 102 |

|      |       | 9.2.2. The adapted algorithm                                 | 103 |

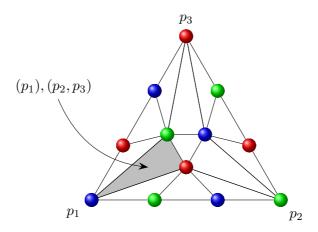

|      | 9.3.  | Iterated immediate snapshot                                  | 104 |

|      |       | 9.3.1. IIS is equivalent to read-write                       | 104 |

|      |       | 9.3.2. Geometric representation of IIS                       | 107 |

|      |       |                                                              |     |

| IV.  | Со    | nsensus objects                                              | 109 |

| 10   | .Con  | sensus and universal construction                            | 111 |

|      | 10.1. | What cannot be read-write implemented                        | 111 |

|      |       | 10.1.1. The case of one dequeuer                             | 111 |

|      |       | 10.1.2. Two or more dequeuers                                |     |

|      | 10.2. | Universal objects and consensus                              |     |

|      |       | A wait-free universal construction                           |     |

|      |       | 10.3.1. Deterministic objects                                |     |

| 11   | Con   | sensus number and the consensus hierarchy                    | 115 |

|      |       | Consensus number                                             | _   |

|      |       | Preliminary definitions                                      |     |

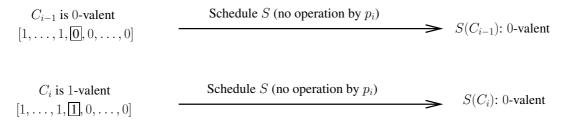

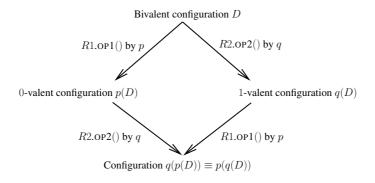

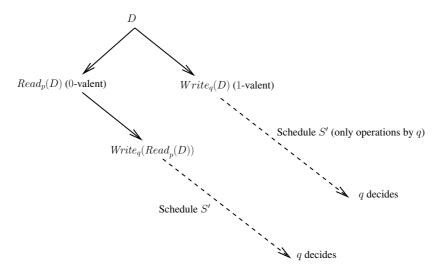

|      | 11,4, | 11.2.1. Schedule, configuration and valence                  |     |

|      |       | 11.2.2. Bivalent initial configuration                       |     |

|      |       | 11.2.2. Divalent findat configuration                        | 110 |

|    | 11.3. | The weak wait-free power of atomic registers                            | 117 |

|----|-------|-------------------------------------------------------------------------|-----|

|    |       | 11.3.1. The consensus number of atomic registers is 1                   | 118 |

|    | 11.4. | Objects whose consensus number is 2                                     | 120 |

|    |       | 11.4.1. Consensus from a test&set objects                               | 120 |

|    |       | 11.4.2. Consensus from queue objects                                    |     |

|    |       | 11.4.3. Consensus from swap objects                                     | 122 |

|    |       | 11.4.4. Other objects for consensus in a system of two processes        |     |

|    |       | 11.4.5. Power and limit of the previous objects                         |     |

|    |       | Objects whose consensus number is $+\infty$                             |     |

|    |       | 11.5.1. Consensus from compare&swap objects                             |     |

|    |       | 11.5.2. Consensus from mem-to-mem-swap objects                          |     |

|    |       | 11.5.3. Consensus from augmented queue objects                          |     |

|    |       | Hierarchy of atomic objects                                             |     |

|    |       | 11.6.1. From consensus numbers to a hierarchy                           |     |

|    |       | 11.6.2. Robustness of the hierarchy                                     |     |

|    |       | 11.012. Roodstiess of the inertainty                                    | 120 |

|    |       |                                                                         |     |

| V. | Sch   | nedulers                                                                | 127 |

|    |       |                                                                         |     |

| 12 |       |                                                                         | 129 |

|    | 12.1. | Solving problems with failure detectors                                 | 129 |

|    |       | 12.1.1. Failure patterns and failure detectors                          | 129 |

|    |       | 12.1.2. Algorithms using failure detectors                              | 130 |

|    |       | 12.1.3. Runs                                                            | 131 |

|    |       | 12.1.4. Consensus                                                       | 131 |

|    |       | 12.1.5. Implementing and comparing failure detectors                    | 131 |

|    |       | 12.1.6. Weakest failure detector                                        | 132 |

|    |       | Extracting $\Omega$                                                     |     |

|    |       | 12.2.1. Overview of the Reduction Algorithm                             | 132 |

|    |       | 12.2.2. DAGs                                                            |     |

|    |       | 12.2.3. Asynchronous simulation                                         |     |

|    |       | 12.2.4. BG-simulation                                                   |     |

|    |       | 12.2.5. Using consensus                                                 |     |

|    |       | 12.2.6. Extracting $\Omega$                                             |     |

|    |       | Implementing $\Omega$ in an eventually synchronous shared memory system |     |

|    |       | 12.3.1. Introduction                                                    |     |

|    |       | 12.3.2. An omega construction                                           |     |

|    |       | 12.3.3. Proof of correctness                                            |     |

|    |       | 12.3.4. Discussion                                                      |     |

|    |       | Bibliographic Notes                                                     |     |

|    | 12    | Dionographic Trocos                                                     |     |

| 13 | .Resi | lience                                                                  | 145 |

|    | 13.1. | Pre-agreement with Commit-Adopt                                         | 145 |

|    |       | 13.1.1. Wait-free commit adopt implementation                           |     |

|    |       | 13.1.2. Using commit-adopt                                              |     |

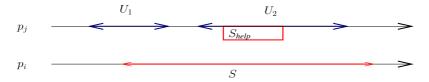

|    |       | Safe Agreement and the power of simulation                              |     |

|    |       | 13.2.1. Solving safe agreement                                          |     |

|    |       | 13.2.2. BG-simulation                                                   |     |

|    |       |                                                                         |     |

| . Adversaries                                                       | 149 |

|---------------------------------------------------------------------|-----|

| 14.1. Non-uniform failure models                                    | 149 |

| 14.2. Background                                                    | 151 |

| 14.2.1. Model                                                       | 151 |

| 14.2.2. Tasks                                                       | 152 |

| 14.2.3. The Commit-Adopt protocol                                   | 152 |

| 14.2.4. The BG-simulation technique                                 | 153 |

| 14.3. Non-uniform failures in shared-memory systems                 | 153 |

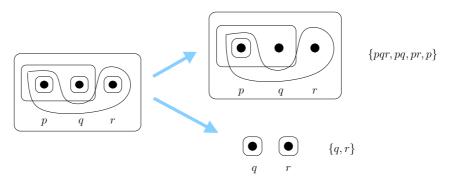

| 14.3.1. Survivor sets and cores                                     | 153 |

| 14.3.2. Adversaries                                                 | 154 |

| 14.3.3. Failure patterns and environments                           | 154 |

| 14.3.4. Asymmetric progress conditions                              | 155 |

| 14.4. Characterizing superset-closed adversaries                    | 155 |

| 14.4.1. A topological approach                                      | 155 |

| 14.4.2. A simulation-based approach                                 | 157 |

| 14.5. Measuring the Power of Generic Adversaries                    | 158 |

| 14.5.1. Solving consensus with $A_{BM}$                             | 158 |

| 14.5.2. Disagreement power of an adversary                          | 158 |

| 14.5.3. Defining <i>setcon</i>                                      | 159 |

| 14.5.4. Calculating $setcon(A)$ : examples                          | 159 |

| 14.5.5. Solving consensus with $setcon = 1 \dots \dots \dots \dots$ | 160 |

| 14.5.6. Adversarial partitions                                      | 161 |

| 14.5.7. Characterizing colorless tasks                              | 161 |

| 14.6. Non-uniform adversaries and generic tasks                     | 162 |

| 14.7. Bibliographic notes                                           | 163 |

# 1. Introduction

In 1926, Gilbert Keith Chesterton published a novel "The Return of Don Quixote" reflecting the advancing industrialization of the Western world, where mass production started replacing personally crafted goods. One of the novel's characters, soon to be converted in a modern version of Don Quixote, says:

"All your machinery has become so inhuman that it has become natural. In becoming a second nature, it has become as remote and indifferent and cruel as nature. ... You have made your dead system on so large a scale that you do not yourselves know how or where it will hit. That's the paradox! Things have grown incalculable by being calculated. You have tied men to tools so gigantic that they do not know on whom the strokes descend."

Since mid-1920s, we made a huge progress in 'dehumanizing' machinery, and computing systems are among the best examples. Indeed, modern large-scale distributed software systems are often claimed to be the most complicated artifacts ever existed. This complexity triggers a perspective on them as natural objects. This is, at the very least, worrying. Indeed, given that our daily life relies more and more upon computing systems, we should be able to understand and control their behavior.

In 2003, almost 80 years after the Chesterton's book was published, Leslie Lamport, in his invited lecture "Future of Computing: Logic or Biology", called for a reconsideration of the general perception of computing:

"When people who can't think logically design large systems, those systems become incomprehensible. And we start thinking of them as biological systems. And since biological systems are too complex to understand, it seems perfectly natural that computer programs should be too complex to understand.

We should not accept this. "

In this book, we intend to support this point of view by presenting a consistent collection of basic comprehensive results in concurrent computing. Concurrent systems are treated here as logical entities with clears goals and strategies.

# 1.1. A broad picture: the concurrency revolution

The field of *concurrent computing* has gained a huge importance after major chip manufacturers have switched their focus from increasing the speed of individual processors to increasing the number of processors on a chip. The good old times where nothing needed to be done to boost the performance of programs, besides changing the underlying processors, are over. To exploit multicore architectures, programs have to be executed in a concurrent manner. In other words, the programmer has to design a program with more and more threads and make sure that concurrent accesses to shared data do not create inconsistencies. A single-threaded application can for instance exploit at most 1/100 of the potential throughput of a 100-core chip.

The computer industry is thus calling for a software revolution: the *concurrency revolution*. This might look surprising at first glance for the very idea of concurrency is almost as old as computer science. In fact, the revolution is more than about concurrency alone: it is about *concurrency for everyone*.

Concurrency is going out of the small box of specialized programmers and is conquering the masses now. Somehow, the very term "concurrency" itself captures this democratization: we used to talk about "parallelism". Specific kinds of programs designed by specialized experts to clearly involve independent tasks were deployed on parallel architectures. The term "concurrency" better reflects a wider range of programs where the very facts that the tasks executing in parallel compete for shared data is the norm rather than the exception. But designing and implementing such programs in a correct and efficient manner is not trivial.

A major challenge underlying the concurrency revolution is to come up with a *library of abstractions* that programmers can use for general purpose concurrent programming. Ideally, such library should both be usable by programmers with little expertise in concurrent programming as well as by advanced programmers who master how to leverage multicore architectures. The ability of these abstractions to be composed is of key importance, because an application could be the result of assembling independently devised pieces of code.

The aim of this book is to study how to define and build such abstractions. We will focus on those that are considered (a) the most difficult to get right and (b) having the highest impact on the overall performance of a program: *synchronization abstractions*, also called *shared objects* or sometimes *concurrent data structures*.

# 1.2. The topic: shared objects

In concurrent computing, a problem is solved through several processes that execute a set of tasks. In general, and except in so called "embarrassingly parallel" programs, i.e., programs that solve problems that can easily and regularly be decomposed into independent parts, the tasks usually need to synchronize their activities by accessing shared constructs, i.e., these tasks depend on each other. These typically serialize the threads and reduce parallelism. According to Amdahl's law [4], the cost of accessing these constructs significantly impacts the overall performance of concurrent computations. Devising, implementing and making good usage of such synchronization elements usually lead to intricate schemes that are very fragile and sometimes error prone.

Every multicore architecture provides synchronization constructs in hardware. Usually, these constructs are "low-level" and making good usage of them is far from trivial. Also, the synchronization constructs that are provided in hardware differ from architecture to architecture, making concurrent programs hard to port. Even if these constructs look the same, their exact semantics on different machines may also be different, and some subtle details can have important consequences on the performance or the correctness of the concurrent program. Clearly, coming up with a high-level library of synchronization abstractions that could be used across multicore architectures is crucial to the success of the multicore revolution. Such a library could only be implemented in software for it is simply not realistic to require multicore manufacturers to agree on the same high-level library to offer to their programmers.

We assume a small set of low-level synchronization primitives provided in hardware, and we use these to implement higher level synchronization abstractions. As pointed out, these abstractions are supposed to be used by programmers of various skills to build application pieces that could themselves be used within a higher-level application framework.

The quest for synchronization abstractions, i.e., the topic of this book, can be viewed as a continuation of one of the most important quests in computing: programming *abstractions*. Indeed, the History of computing is largely about devising abstractions that encapsulate the specifities of underlying hardware and help programmers focus on higher level aspects of software applications. A *file*, a *stack*, a *record*, a *list*, a *queue* and a *set*, are well-known examples of abstractions that have proved to be valuable in traditional sequential and centralized computing. Their definitions and effective implementations have

enabled programming to become a high-level activity and made it possible to reason about algorithms without specific mention of hardware primitives.

In modern computing, an abstraction is usually captured by an *object* representing a server program that offers a set of operations to its users. These operations and their specification define the behavior of the object, also called the *type* of the object.

The way an abstraction (object) is implemented is usually hidden to its users who can only rely on its operations and their specification to design and produce upper layer software, i.e., software using that object. The only visible part of an object is the set of values in can return when its operations are invoked. Such a modular approach is key to implementing provably correct software that can be reused by programmers in different applications.

The abstractions we study in this book are *shared* objects, i.e., objects that can be accessed by concurrent processes, typically running on independent processors. That is, the operations exported by the shared object can be accessed by concurrent processes. Each individual process accesses however the shared object in a sequential manner. Roughly speaking, sequentiality means here that, after it has invoked an operation on an object, a process waits to receive a reply indicating that the operation has terminated, and only then is allowed to invoke another operation on the same or a different object. The fact that a process p is executing an operation on a shared object p does not however preclude other processes p from invoking an operation on the same object p.

The objects considered have a precise *sequential specification*. called also its *sequential type*, which specifies how the object behaves when accessed sequentially by the processes. That is, if executed in a sequential context (without concurrency), their behavior is known. This behavior might be deterministic in the sense that the final state and response is uniquely defined given every operation, input parameters and initial state. But this behavior could also be non-deterministic, in the sense that given an initial state of the object, and operation and an input parameter, there can be several possibilities for a new state and response.

To summarize, this book studies how to implement, in the algorithmic sense, objects that are shared by concurrent processes. Strictly speaking, the objective is to implement object types but when there is no ambiguity, we simply say objects. In a sense, a process represents a sequential Turing machine, and the system we consider represents a set of sequential Turing machines. These Turing machines communicate and synchronize their activities through low-level shared objects. The activities they seek to achieve consist themselves in implementing higher-level shared objects. Such implementations need to be *correct* in the sense that they typically need to satisfy two properties: *linearizability* and *wait-freedom*. We now overview these two properties before detailing them later.

# 1.3. Linearizability

This property says that, despite concurrency among operations of an object, these should appear as if they were executed sequentially. Two concepts are important here. The first is the notion of appearance, which, as we already pointed out, is related to the values returned by an operation: these values are the only way through which the behavior of an object is visible to the users of that object, i.e., the applications using that object. The second is the notion of sequentiality which we also discussed earlier. Namely, The operations issued by the processes on the shared objects should appear, according to the values they return, as if they were executing one after the other. Each operation invocation op on an object X should appear to take effect at some indivisible instant, called the linearization point of that invocation, between the invocation and the reply times of op.

In short, linearizabiliy delimits the scope of an object operation, namely what it could respond in a concurrent context, given the sequential specification of that object. This property, also sometimes called *atomicity*, transforms the difficult problem of reasoning about a concurrent system into the simpler problem of reasoning about a sequential one where the processes access each object one after the other. Linearizability constraints the implementation of the object but simplifies its usage on the other hand. To program with linearizable objects, also called atomic objects, the developer simply needs the *sequential specification* of each object, i.e., its sequential type.

Most interesting synchronization problems are best described as linearizable shared objects. Examples of popular synchronization problems are the *reader-writer* and the *producer-consumer* problems. In the reader-writer problem, the processes need to read or write a shared data structure such that the value read by a process at a given point in time t is the last value written before t. Solving this problem boils down to implementing a linearizable object exporting read() and write() operations. Such an object type is usually called a linearizable, an atomic read-write variable or a register. It abstracts the very notions of shared file and disk storage.

In the producer-consumer problem, the processes are usually split into two camps: the producers which create items and the consumers which use the items. It is typical to require that the first item produced is the first to be consumed. Solving the producer-consumer problem boils down to implementing a linearizable object type, called a FIFO queue (or simply a queue) that exports two operations: enqueue() (invoked by a producer) and dequeue() (invoked by a consumer).

Other exemples include for instance *counting*, where the problem consists in implementing a shared counter, called FAI Fetch - and - Increment. Processes invoque this object to increment the value of the counter and get the current value.

# 1.4. Progress

This property basically says that processes should not prevent each other from obtaining values to their operations. More specifically, no process p should ever prevent any other process q from making progress, i.e., obtaining responses to q's operations, provided q remains alive and kicking. A process q should be able to terminate each of its operations on a shared object X despite speed variations or the failure of any other process p. Process p could be very fast and might be permanently accessing shared object X, or could have been swapped out by the operating system while accessing X. None of these situations should prevent q from completing its operation. Wait-freedom conveys the *robustness* of an implementation. It transforms the difficult problem of reasoning about a failure-prone system where processes can be arbitrarily delayed or speeded up, into the simpler problem of reasoning about a system where every process progresses at its own pace and runs to completion.

In other words, wait-freedom says that the process invoking the operation on the object should obtain a response for the operation, in a finite number of its own *steps*, independently of concurrent steps from other processes. The notion of step, as we will discuss later, means here a local instruction of the process, say updating a local variable, or an operation invocation on a base object (low-level object) used in the implementation.

# 1.5. Combining linearizability and wait-freedom

Ensuring each of linearizability alone or wait-freedom alone is simple. A trivial wait-free implementation could return arbitrary responses to each operation, say some value corresponding to some initial state of the object. This would satisfy wait-freedom as no process would prevent other processes from progressing. However, the responses would no satisfy linearizability.

Also, one could ensure linearizability using a basic *mutual exclusion* mechanism so that every operation on the implemented object is performed in an indivisible critical section. Some traditional synchro-

nization schemes rely indeed on *mutual exclusion* (usually based on some *locking* primitives): critical shared objects (or critical sections of code within shared objects) are accessed by processes one at a time. No process can enter a critical section if some other process is in that critical section. We also say that a process has acquired a *lock* on that object (resp., critical section). Linearizability is then automatically ensured if all related variables are protected by the same critical section. This however significantly limits the parallelism and thus the performance of the program, unless the program is devised with minimal interference among processes. Mutual exclusion hampers progress since a process delayed in a critical section prevents all other processes from entering that critical section. In other words, it violates wait-freedom. Delays could be significant and especially when caused by crashes, preemptions and memory paging. For instance, a process paged-out might be delayed for millions of instructions, and this would mean delaying many other processes if these want to enter the critical section held by the delayed process. With modern architectures, we might be talking about one process delaying hundreds of processors, making them completely idle and useless. We will study other, weaker *lock-free* implementations, which also provide an alternative to mutual exclusion-based implementations.

# 1.6. Object implementations

As explained, this book studies how to wait-free implement high-level atomic objects out of more primitive base objects. The notions of *high* and *primitive* being of course relative as we will see. It is also important to notice that the term *implement* is to be considered in an abstract manner; we will describe the algorithms in pseudo-code. There will not be any C or Java code in this book. A concrete execution of these algorithms would need to go through a translation into some programming language.

An object to be implemented is typically called *high-level*, in comparison with the objects used in the implementation, considered at a *lower-level*. It is common to talk about *emulations* of the high-level object using the low-level ones. Unless explicitly stated otherwise, we will by default mean *wait-free implementation* when we write *implementation*, and *atomic object* when we write *object*.

It is often assumed that the underlying system model provides some form of *registers* as base objects. These provide the abstraction of read-write storage elements. Message-passing systems can also, under certain conditions, emulate such registers. Sometimes the base registers that are supported are atomic but sometimes not. As we will see in this book, there are algorithms that implement atomic registers out of non-atomic base registers that might be provided in hardware.

Some multiprocessor machines also provide objects that are more powerful than registers like *test&set* objects or *compare&swap* objects. Intuitively, these are more powerful in the sense that the writer process does not systematically overwrite the state of the object, but specifies the conditions under which this can be done. Roughly speaking, this enables more powerful synchronization schemes than with a simple register object. We will capture the notion of "more powerful" more precisely later in the book.

Not surprisingly, a lot of work has been devoted over the last decades to figure out whether certain objects can wait-free implement other objects. As we have seen, focusing on wait-free implementations clearly excludes mutual exclusion (locking) based approaches, with all its drawbacks. From the application perspective, there is a clear gain because relying on wait-free implementations makes it less vulnerable to failures and dead-locks. However, the desire for wait-freedom makes the design of atomic object implementations subtle and difficult. This is particularly so when we assume that processes have no *a priori* information about the interleaving of their steps: this is the model we will assume by default in this book to seek general algorithms.

# 1.7. Reducibility

In its abstract form, the question we address in this book, namely of implementing high-level objects using lower level objects, can be stated as a general *reducibility* question. Given two object types X1 and X2, can we implement X2 using any number of instances of X1 (we simply say "using X1")? In other words, is there an algorithm that implements X2 using X1? In the case of concurrent computing, "implementing" typically assumes providing linearizability and wait-freedom. These notions encapsulate the smooth handling of concurrency and failures.

When the answer to the reducibility question is negative, and it will be for some values of X1 and X2, it is also interesting to ask what is needed (under some minimality metric) to add to the low-level objects (X1) in order to implement the desired high-level object (X2). For instance, if the base objects provided by a given multiprocessor machine are not enough to implement a particular object in software, knowing that extending the base objects with another specific object (or many of such objects) is sufficient, might give some useful information to the designers of the new version of the multiprocessor machine in question. We will see examples of these situations.

# 1.8. Organization

The book is organized in an incremental way, starting from very basic objects, then going step by step to implementing more and more sophisticated and powerful objects. After precisely defining the notions of linearizability and wait-freedom, we proceed through the following steps.

- 1. We first study how to implement linearizable read-write registers out of non-linearizable base registers, i.e., registers that provide weaker guarantees than linearizability. Furthermore, we show how to implement registers that can contain values from an arbitrary large range, and be read and written by any process in the system, starting from single-bit (containing only 0 or 1) base registers, where each base register can be accessed by only one writer process and only one reader process.

- 2. We then discuss how to use registers to implement seemingly more sophisticated objects than registers, like *counters* and *snapshot* objects. We contrast this with the inherent limitation of linearizable registers in implementing more powerful objects like *queues*. This limitation is highlighted through the seminal *consensus impossibility* result.

- 3. We then discuss the importance of consensus as an object type, by proving its *universality*. In particular, we describe a simple algorithm that uses registers and consensus objects to implement any other object. We then turn to the question on how to implement a consensus object from other objects. We describe an algorithm to implement a consensus object in a system of two processes, using registers and either a test&set or a queue objects, as well as an algorithm that implements a consensus object using a compare&swap object in a system with an arbitrary number of processes. The difference between these implementations is highlighted to introduce the notion of *consensus number*.

- 4. We then study a complementary way of implementing consensus: using registers and specific oracles that reveal certain information about the operational status of the processes. Such oracles can be viewed as *failure detectors* providing information about which process are operational and which processes are not. We discuss how even an oracle that is unreliable most of time can help devise a consensus algorithm. We also discuss the implementation of such an oracle assuming that the computing environment satisfies additional assumptions about the scheduling

of the processes. This may be viewed as a slight weakening of the wait-freedom requirement which requires progress no matter how processes interleave their steps.

# 1.9. Bibliographical notes

The fundamental notion of abstract object type has been developed in various textbooks on the theory or practice of programming. Early works on the genesis of abstract data types were described in [22, 66, 74, 73]. In the context of concurrent computing, one of the earliest work was reported in [16, 72]. More information on the history concurrent programming can be found in [14].

The notion of register (as considered in this book) and its formalization are due to Lamport [63]. A more hardware-oriented presentation was given in [71]. The notion of atomicity has been generalized to any object type by Herlihy and Wing [51] under the name linearizability. The concept of snapshot object has been introduced in [1]. A theory of wait-free atomic objects was developed in [55].

The classical (non-robust) way to ensure linearizability, namely through mutual exclusion, has been introduced by Dijkstra [25]. The problem constituted a basic chapter in nearly all textbooks devoted to operating systems. There was also an entire monograph solely devoted to the mutual exclusion problem [77]. Various synchronization algorithms are also detailed in [80].

The notion of wait-free computation originated in the work of Lamport [60], and was then explored further by Peterson [76]. It has then been generalized and formalized by Herlihy [42].

The consensus problem was introduced in [75]. Its impossibility in asynchronous message-passing systems prone to process crash failures has been proved by Fischer, Lynch and Paterson in [30]. Its impossibility in shared memory systems was proved in [68]. The universality of the consensus problem and the notion of consensus number were investigated in [42].

The concept of failure detector oracle has been introduced by Chandra and Toueg [18]. An introductory survey to failure detectors can be found in [31].

# Part I. Correctness

# 2. Linearizability

#### 2.1. Introduction

Linearizability is a metric of the correctness of a shared object implementation. It addresses the question of what values can be returned by an object that is shared by concurrent processes. If an object returns a response, linearizability says whether this response is *correct* or not.

The notion of *correctness*, as captured by linearizability, is defined with respect to how the object is expected to behave when accessed sequentially (e.g., when the object is not shared): this is called the *sequential specification* of the object. In this sense, the notion of correctness of an object, as captured by linearizability, is *relative* to correctness in a sequential context.

It is important to notice that linearizability does not say when an object is expected to return a response. As we will see later, the complementary property to linearizability is *wait-freedom*, another correctness metric that captures the fact that an object operation *should* eventually return a response (if certain conditions are met).

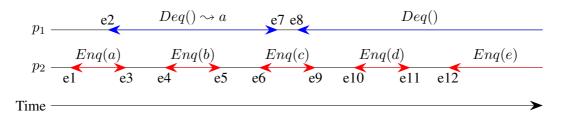

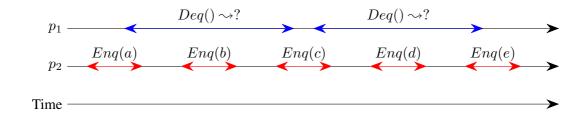

To illustrate the notion of linearizability, and the actual relation to a sequential specification, consider a FIFO (first-in-first-out) queue. This is an object of the type queue that contains an ordered set of elements and exhibits the following two operations to manipulate this set.

- Enq(a): Insert element a at the end of the queue;

- Deq(): Return the first element inserted in the queue that was not already removed; Then remove this element from the queue; if the queue is empty, return the default element  $\perp$ .

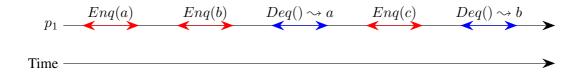

Figure 2.1.: Sequential execution of a queue

Figure 2.1 conveys a sequential execution of a single process accessing the queue (here the time line goes from left to right). There is only a single object and a single process the process first enqueues element a, then element b, and finally element c. According to the expected semantics of a queue (first-in-first-out), and as depicted by the figure, the first dequeue invocation returns element a whereas the second returns element a.

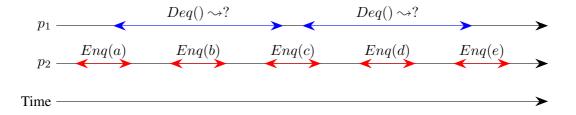

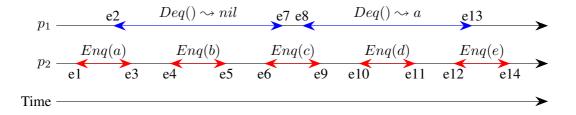

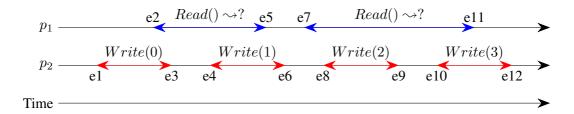

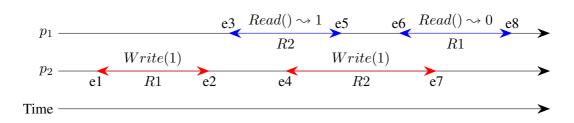

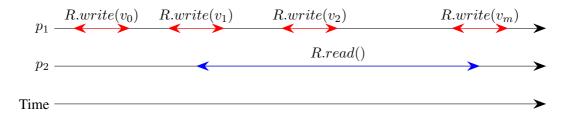

Figure 2.2 depicts a concurrent execution of two processes sharing the same queue:  $p_1$  and  $p_2$ . Process  $p_2$ , acting as a producer, enqueues elements a, b, c, d, and then e. On the other hand, process  $p_1$ , acting as a consumer, seeks to dequeue two elements. On Figure 2.2, the execution of Enq(a), Enq(b) and Enq(c) by  $p_2$  overlaps with the first Deq() of  $p_1$ , whereas the execution of Enq(d), Enq(e) and Enq(f) by  $p_2$  overlaps with the second Deq() of  $p_1$ . The role of linearizability is precisely to address the questions raised by Figure 2.2, namely, what elements could be dequeued by  $p_1$ ?

Figure 2.2.: Concurrent execution of a queue

Linearizability answers these questions by relying on how the queue is supposed to behave if accessed sequentially. In other words, what should happen in Figure 2.2 depends on what happens in Figure 2.1.

Intuitively, linearizability says that, when accessed concurrently, an object should return the same values that it could have returned in some legal sequential execution. Before defining linearizability however, and the very concept of "value that could have been returned in some legal sequential execution", we first define more precisely the important players involved in the execution, namely processes and objects, and then the very notion of a sequential specification.

# 2.2. The Players

#### 2.2.1. Processes

We consider a system consisting of a finite set of n processes, denoted  $p_1, \ldots, p_n$ . Besides accessing local variables, processes may execute operations on *shared objects* (we will sometimes simply say *objects*). Through these objects, the processes *synchronize* their computations. In the context of this chapter, we omit the local variables accessed by the processes since we are interested in their external behavior.

An execution by a process of an operation on a object X is denoted X.op(arg)(res) where arg and res denote, respectively, the input and output parameters of the operation invocation. The output corresponds to the response to the invocation. It is common to write X.op when the input and output parameters are not important.

The execution of an operation op() on an object X by a process  $p_i$  is modeled by two events, namely, (1) the events denoted inv[X.op(arg)] by  $p_i$  that occurs when  $p_i$  invokes the operation (invocation event), and (2) the event denoted resp[X.op(res)] by  $p_i$  that occurs when the operation terminates (response event). We say that these events are generated by process  $p_i$  and associated with object X. Given an operation X.op(arg)(res), the event resp[X.op(res)] by  $p_i$  is called the response event matching the invocation event inv[X.op(arg)] by  $p_i$ . Sometimes, when there is no ambiguity, we talk about operations where we should be talking about operation executions. We also say sometimes that the object returns a response to the process. This is by language abuse because it is actually the process executing the operation on the object that actually computes the response.

Every interaction between a process and an object corresponds to a computation *step* and is represented by an *event*: the visible part of a step, i.e., the invocation (request) or the response (reply) of an operation. A sequence of such events is called a *history* and this is precisely how we model executions of processes on shared objects. Basically, a history depicts the sequence of observable events of the execution of a concurrent system. We will detail the very notion of history later in this chapter.

Whilst we assume that the system of processes is *concurrent*, we assume that each process is individually *sequential*: a process executes (at most) one operation on an object at a time. That is, the algorithm

of a sequential process stipulates here that, after an operation is invoked on an object, and until a matching response is returned, the process does not invoke any other operation. As pointed out, the fact that processes are (individually) sequential does not preclude them from concurrently invoking operations on the same shared object. Sometimes however, we will focus on *sequential executions* (modeled by *sequential histories*) which precisely preclude such concurrency; that is, only one process at a time invokes an operation on an object.

#### 2.2.2. Objects

An object has a unique *identity* and is of a unique *type*. Multiple objects can be of the same type however: we talk about *instances* of the type. In our context, we consider a type as defined by (1) the set of possible values for (the states of) objects of that type, including the *initial* state; (2) a finite set of operations through which the (state of the) objects of that type can be manipulated; and (3) a *sequential specification* describing, for each operation of the type, the effect this operation produces when it executes alone on the object, i.e., in the absence of concurrency. The effect is basically the response that the object returns and the new state of the object gets after the operation executes.

We assume here that every operation of an object type can be applied on each of its states. This sometimes requires specific care when defining the objects. For instance, if a dequeue operation is invoked on a queue which is in an empty state, a specific response *nil* is returned.

We say that an object operation is *deterministic* if, given any state of the object and input parameters, the response and the resulting state of the object are *uniquely* defined. An object type is deterministic if it has only deterministic operations. We assume here *finite* non-determinism, i.e., for each state and operation, the set of possible outcomes (response and resulting state) is finite. Otherwise the object is said to be *non-deterministic*: several outputs and resulting states are possible. The pair composed of (a) the output returned and (b) the resulting state, is chosen randomly from the set of such possible pairs (or from an infinite set).

A sequential specification is modeled as a set of sequences of invocations immediately followed by matching responses that, starting from an initial state of an object, are allowed by the object (type) when it is accessed sequentially. Indeed the resulting state obtained after each operation execution is not directly conveyed, but it is indirectly reflected through the responses returned in the subsequence operations of the sequence.

To illustrate the notion of a sequential specification, consider the following two object types:

**Example 1: a FIFO queue** The first example is the unbounded (FIFO) queue described earlier. The producer enqueues items in a queue that the consumers dequeues. The queue type has the following sequential specification: every dequeue returns the first element enqueued and not dequeued yet. If there is not such element (i.e., the queue is empty), a specific default value *nil* is returned. As pointed out earlier this specification never prevents an enqueue or a dequeue operation to be executed. One could consider a variant of the specification where the dequeue could not be executed if the queue is empty it would have to wait for an enqueue - we preclude such specifications.

Designing algorithms that implement this object correctly in a concurrent context captures the classical *producer/consumer* synchronization problem.

**Example 2: a read/write object (register)** The second example (called register) is a simple read/write abstraction that models objects such as a shared memory word, a shared file or a shared disk. Designing algorithms that implement this object correctly in a concurrent context captures the classical *reader/writer* synchronization problem.

The type exports two operations:

- The operation read() has no input parameter. It returns the value stored in the object.

- The operation write(v) has an input parameter, v, representing the new value of the object. This operation returns value ok indicating to the calling process that the operation has terminated.

The sequential specification of the object is defined by all the sequences of read and write operations in which each read operation returns the input parameter of the last preceding write operation (i.e., the last value written). We will study implementations of this object in the next chapters.

#### 2.2.3. Histories

Processes interact with shared objects via invocation and response events. Such events are totally ordered. (Simultaneous events are arbitrarly ordered).

The interaction between processes and objects is thus modeled as a totally ordered set of events H, called a *history* (sometimes also called a *trace*). The total order relation on H, denoted  $<_H$ , abstracts out the real-time order in which the events actually occur.

Recall that an event includes (a) the name of an object, (b) the name of a process, (c) the name of an operation as well as the corresponding input or output parameters.

A *local* history of  $p_i$ , denoted  $H|p_i$ , is a projection of H on process  $p_i$ : the subsequence H consisting of the events generated by  $p_i$ .

Two histories H and H' are said to be *equivalent* if they have the same local histories, i.e., for each process  $p_i$ ,  $H|p_i = H'|p_i$ .

As we consider sequential processes, we focus on histories H such that, for each process  $p_i$ ,  $H|p_i$  (the local history generated by  $p_i$ ) is sequential: the history starts with an invocation, followed by a response, (the matching response associated with the same object) followed by another invocation, etc. We say in this case that the global history H is well-formed.

An operation is said to be *complete* in a history if the history includes both the event corresponding to the invocation of the operation and its response. If the history contains only the invocation, we say that the operation is *pending* in that history. A history without pending operations is said to be *complete*. A history with pending operations is said to be *incomplete*. Incomplete histories are important to study as they typically model the situation where a process invokes an operation and stops, e.g., crashes, before obtaining a response. Note that, being sequential, a process can have at most one pending operation in a given history.

A history H induces an irreflexive partial order on its operations. Let op = X.op1() by  $p_i$  and op' = Y.op2() by  $p_j$  be two any operations. Informally, operation op precedes operation op', if op terminates before op' starts, where "terminates" and "starts" refer to the time-line abstracted by the  $<_H$  total order relation. More precisely:

$$(op \rightarrow_H op') \stackrel{\text{def}}{=} (resp[op] <_H inv[op']).$$

Two operations op and op' are said to overlap (we also say they are concurrent) in a history H if neither  $resp[op] <_H inv[op']$ , nor  $resp[op'] <_H inv[op]$  (neither precedes the other one). Notice that two overlapping operations are such that  $\neg(op \rightarrow_H op')$  and  $\neg(op' \rightarrow_H op)$ . As sequential histories have no overlapping operations,  $\rightarrow_H$  is a total order if H is a sequential history.

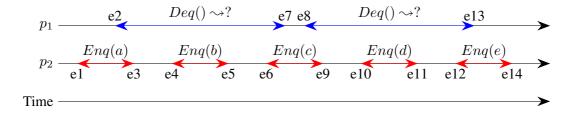

Figure 2.3 highlights the events involved in the history depicting the execution of Figure 2.2. The history of Figure 2.3 contains events  $e_1 \dots e_{14}$ . As all events in H involve the same object, the identity of this object is omitted. The history has no pending operations, and is consequently complete.

If we restrict the history to the sequence of events  $e_1 \dots e_{12}$ , we will obtain an incomplete one: the last dequeue operation of  $p_1$  as well as the last enqueue of  $p_2$  are now pending operations in the resulting

Figure 2.3.: Queue history

history.

#### 2.2.4. Sequential histories

**Definition 1** A history is sequential if its first event is an invocation, and then (1) each invocation event, except possibly the last, is immediately followed by the matching response event, (2) each response event, except possibly the last, is immediately followed by an invocation event.

The precision "except possibly the last" is due to the fact that a history can be incomplete as we discussed earlier. A history that is not sequential is said to be *concurrent*.

Given that a sequential history S has no overlapping operations, the associated partial order  $\rightarrow_S$  defined on its operations is actually a total order. Strictly speaking, the sequential specification of an object is a set of sequential histories involving solely that object. Basically, the sequential specification represents all possible sequential accesses to the object.

Figure 2.4.: Example of a sequential history

Figure 2.4 depicts a complete sequential history. This history has no overlapping operations. The operations are totally ordered.

#### 2.2.5. Legal histories

As we pointed out, the definition of a linearizable history refers to the sequential specifications of the objects involved in the history. The notion of a *legal* history captures this idea.

Given a sequential history H and an object X, let H|X denote the subsequence of H made up of all the events involving only object X. We say that H is legal if, for each object X involved in H, H|X belongs to the sequential specification of X. Figure 2.4 for instance depicts a legal history. It belongs to the sequential specification of the queue. The first dequeue by  $p_1$  returns a  $p_2$  whereas the second returns a  $p_2$ .

# 2.3. Linearizability

Intuitively, linearizability states that a history is correct if the response returned to its invocations could have been obtained by a sequential execution, i.e., according to the sequential specifications of the objects. More specifically, we say that a history is linearizable if each operation appears as if it has been executed instantaneously at some indivisible point between its invocation event and its response event. This point is called the *linearization point* of the operation. We define below more precisely linearizability as well as some of its main characteristics.

#### 2.3.1. The case of complete histories

For pedagogical reasons, it is easier to first define linearizability for complete histories H, i.e., histories without pending operations, and then extend this definition to incomplete histories.

**Definition 2** A complete history H is linearizable if there is a history L such that:

- 1. H and L are equivalent,

- 2. L is sequential,

- 3. L is legal, and

- 4.  $\rightarrow_H \subseteq \rightarrow_L$ .

The definition above says that a history H is linearizable if there exist a permutation of H, L, which satisfies the following requirements. First, L has to be indistinguishable from H to any process: this is the meaning of equivalence. Second, L should not have any overlapping operations: it has to be sequential. Third, the restriction of L to every object involved in it should belong to the sequential specification of that object: it has to be legal. Finally, L has to respect the real-time occurrence order of the operations in H.

In short, L represents a history that could have been obtained by executing all the operations of H, one after the other, while respecting the occurrence order of non-overlapping operations in H. Such a sequential history L is called a *linearization* of H or a *sequential witness* of H.

An algorithm implementing some shared object is said to be linearizable if all histories generated by the processes accessing the object are linearizable. Proving linearizability boils down to exhibiting, for every such history, a linearization of the history that respects the "real-time" occurrence order of the operations in the history, and that belongs to the sequential specification of the object. This consists in determining for every operation of the history, its linearization point in the corresponding sequential witness history. To respect the real time occurrence order, the linearization point associated with an operation has always to appear within the interval defined by the invocation event and the response event associated with that operation. It is also important to notice that a history H, may have multiple possible linearizations.

**Example with a queue.** Consider history H depicted on Figure 2.3. Whether H is linearizable or not depends on the values returned by the dequeue invocations of  $p_1$ , i.e., in events  $e_7$  and  $e_{13}$ . For example, assuming that the queue is initially empty, two possible values are possible for  $e_7$ : a and nil.

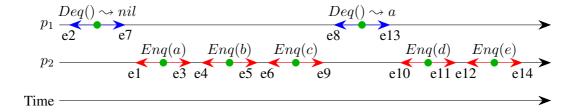

1. In the first case, depicted on Figure 2.5, the linearization of the first dequeue of  $p_1$  would be before the first enqueue of  $p_2$ . We depict the linearization, and the corresponding linearization points on Figure 2.6.

Figure 2.5.: The first example of a linearizable history with a queue

Figure 2.6.: The first example of a linearization

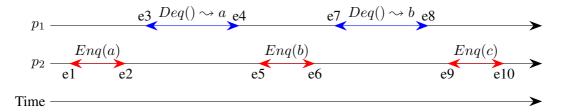

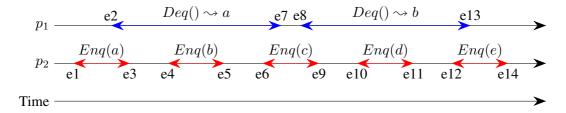

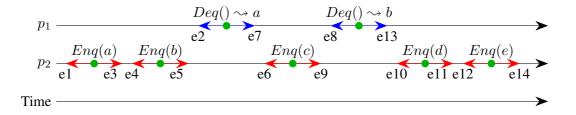

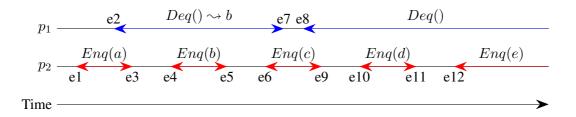

2. In the second case, depicted on Figure 2.7, the linearization of the first dequeue of  $p_1$  would be after the first enqueue of  $p_2$ . We depict the linearization, and the corresponding linearization points on Figure 2.8.

Figure 2.7.: The second example of a linearizable history with a queue

It is important to notice that, in order to ensure linearizability, the only possible values for  $e_7$  are a and nil. If any other value was returned, the history of Figure 2.7. would not have been linearizable. For instance, if the value was b, i.e., if the first dequeue of  $p_1$  returned b, then we could not have found any possible linearization of the history. Indeed, the dequeue should be linearizable after the enqueue of b, which is after the enqueue of a. To be legal, the linearization should have a dequeue of a before the dequeue of b—a contradiction.

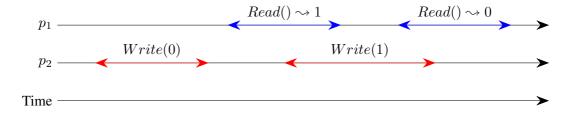

**Example with a register.** Figure 2.9 highlights a history of two processes accessing a shared register. The history contains events  $e_1 \dots e_{12}$ . The history has no pending operations, and is consequently complete.

Assuming that the register initially stores value 0, two possible returned values are possible for  $e_5$  in order for the history to be linearizable: 0 and 1. In the first case, the linearization of the first read of  $p_1$  would be right after the first write of  $p_2$ . In the second case, the linearization of the first read of  $p_1$  would be right after the second write of  $p_2$ .

Figure 2.8.: The second example of linearization

Figure 2.9.: Example of a register history

For the second read of  $p_1$ , the history is linearizable, regardless of whether the second read of  $p_1$  returns values 1, 2 or 3 in event  $e_7$ . If this second read had returned a 0, the history would not be linearizable.

#### 2.3.2. The case of incomplete histories

So far we considered only complete histories. These are histories with at least one process whose last operation is pending: the invocation event of this operation appears in the history while the corresponding response event does not. Extending linearizability to incomplete histories is important as it allows to state what responses are correct when processes crash. We cannot decide when processes crash and then cannot expect from a process to first terminate a pending operation before crashing.

**Definition 3** A history H (whether it is complete or not) is linearizable if H can be completed in such a way that every invocation of a pending operation is either removed or completed with a response event, so that the resulting (complete) history H' is linearizable.

Basically, this definition transforms the problem of determining whether an incomplete history H is linearizable to the problem of determining whether a complete history H', obtained by completing H, is linearizable. H' is obtained by adding response events to certain pending operations of H, as if these operations have indeed been completed, or by removing invocation events from some of the pending operations of H. (All complete operations of H are preserved in H'.) It is important to notice that the term "complete" is here a language abuse as we might "complete" a history by removing some of its pending invocations. It is also important to notice that, given an incomplete history H, we can complete it in several ways and derive several histories H' that satisfy the required conditions.

**Example with a queue.** Figure 2.10 depicts an incomplete history H. We can complete H by adding to it the response b to the second dequeue of  $p_1$  and a response to the second enqueue of  $p_2$ : we would obtain history H' of Figure 2.5 which is linearizable. We could also have "completed" H

by removing any of the pending operations, or both of them. In all cases, we would have obtained a complete history that is linearizable.

Figure 2.10.: A linearizable incomplete history

Figure 2.11.: A non-linearizable incomplete history

Figure 2.11 also depicts an incomplete history. However, no matter how we try to complete it, either by adding responses or removing invocations, there is no way to determine a linearization of the completed history.

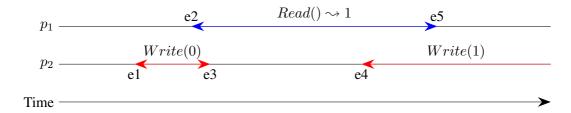

**Example with a register.** Figure 2.12 depicts an incomplete history of a register. The only way to complete the history in order to make it linearizable is to complete the second write of  $p_2$ . This would enable the read of  $p_1$  to be linearized right after it.

Figure 2.12.: A linearizable incomplete history

#### 2.3.3. Completing a linearizable history

An interesting characteristic of linearizability is its *nonblocking* flavour: every pending operation in a history H can be completed without having to wait for any other operation to complete nor sacrificing the linearizability of the resulting history. The following theorem captures this characteristic.

**Theorem 1** Let H be any finite linearizable history and inv[op] any pending operation invocation in H. There is a response r = resp[op] such that  $H \cdot r$  is linearizable.

**Proof** As H is incomplete and linearizable, there is a completion of H, H' that is linearizable, i.e., that has a linearization L. of H. If L contains inv[op] and its matching response r, then L is also linearization of  $H \cdot r$ . If L contains neither inv[op] not r (i.e., H' does not contain inv[op]), then  $L' = L \cdot inv[op] \cdot r$  is a linearization of  $H' \cdot inv[op] \cdot r$ , which means that  $H \cdot r$  is linearizable.  $\square_{Theorem\ 2}$

# 2.4. Composition

A property is a set of histories. A property P is said to be *compositional* if it is enough to prove that it holds for each of the objects of a set in order to prove that it holds for the entire set: for each history H, we have  $\forall X \ H | X \in P$  if and only if  $H \in P$ . Intuitively, compositionality enables to derive the correctness of a composed system from the correctness of the components. This property is crucial for modularity of programming: a correct (linearizable) compositions can be obtained from correct (linearizable) components.

**Theorem 2** A history H is linearizable if and only if, for each object X involved in H, H|X is linearizable.

**Proof** The "only if" direction is an immediate consequence of the definition of linearizability: if H is linearizable then, for each object X involved in H, H|X is linearizable. Indeed, for every linearization S of H, S|X is a linearization of H|X.

To prove the other direction, consider a history H, where for each object X, H|X has a linearization, denoted  $S_X$ , let  $\to_X$  denote the total order in  $S_X$  of the operation on X in H. We show below that the relation  $\to=\bigcup_X\{\to_X\}\cup\{\to_H\}$  does not induce any cycle. This means that its transitive closure is a partial order, and its linear extension S is a linearization of H.

Assume by contradiction that  $\to$  contains a cycle. Recall that  $\to_X$  and  $\to_H$  are transitive. We can thus replace any fragment of the form  $op_1 \to_X op_2 \to_X op_3$  (respectively,  $op_1 \to_H op_2 \to_H op_3$ ) with  $op_1 \to_X op_3$  (respectively,  $op_1 \to_H op_3$ ). Moreover, since every operation concerns exactly one object, the cycle cannot contain fragments of the form  $op_1 \to_X op_2 \to_Y op_3$  for  $X \neq Y$ . Hence, the cycle alternate edges of the form  $\to_X$  with edges  $\to_H$ .

Now consider the fragment  $op_1 \to_H op_2 \to_X op_3 \to_H op_4$ . Recall that  $\to_X$  is the order of operations in  $S_X$ , a linearization of H|X. Since  $S_X$  respect real time, we have  $op_3 \to_X op_2$ , i.e., the invocation of  $op_2$  precedes the response of  $op_3$  in H|X (and, thus, in H). Since  $op_1 \to_H op_2$ , the response of  $op_1$  precedes the invocation of  $op_2$  and, thus, the response of  $op_3$ . Since  $op_3 \to_H op_4$ , the response of  $op_3$  and, thus, the response of  $op_4$  in  $op_4$  in  $op_4$ , i.e., we can shorten the fragment to one edge  $op_4$ . By eliminating all edges of the form  $op_4 \to_A op_4$ , i.e., we obtain a cycle of edges  $op_4 \to_A op_4$  contradiction with the definition of  $op_4 \to_A op_4$  in  $op_4 \to_A op_4$ , i.e., we operations in  $op_4 \to_A op_4$  in  $op_4 \to_A op_4$ , i.e., we operations in  $op_4 \to_A op_4$  in  $op_4 \to_A op_4$ , i.e., we operations in  $op_4 \to_A op_4$  in  $op_4 \to_A op_4$ , i.e., we operations in  $op_4 \to_A op_4$  in  $op_4$

Hence the transitive closure of  $\rightarrow$  is irreflexive and anti-symmetric and, thus, has a linear extension: a total order on operations in H that respects  $\rightarrow_H$  and  $\rightarrow_X$ , for all X. Consider the sequential history S induced by any such total order. Since, for all X,  $S|X=S_X$  and  $S_X$  is legal, S is legal. Since  $\rightarrow_H\subseteq\rightarrow_S$ , S respects the real-time order of H. Finally, since each  $S_X$  is equivalent to a completion of H|X, S is equivalent to a completion of H, where each incomplete operation on an object X is completed in the way it is completed in  $S_X$ . Hence, S is a linearization of H.

#### The importance of real time

Linearizability stipulates correctness with respect to a sequential execution: an operation needs to appear to take effect instantaneously, respecting the sequential specification of the object. In this respect, linearizability is similar to *sequential consistency*, a classical correctness criteria for shared objects. There is however a fundamental difference between linearizability and sequential consistency, and this difference is crucial to making linearizability compositional, which is not the case for sequential consistenty, as we explain below.

Sequential consistency is a relaxation of linearizability. It only requires that the real-time order is preserved if the operations are invoked by the same process, i.e., S is only supposed to respect the *process-order* relation.

More specifically, a history H is sequentially consistent if there is a "witness" history S such that:

- 1. H and S are equivalent,

- 2. S is sequential and legal.

Both linearizability and sequential consistency require a witness sequential history. However, and as we pointed out, sequential consistency has no further requirement related to the occurrence order of operations issued by different processes (and captured by the real-time order). It is based only on a logical time (the one defined by the witness history). In some sense, with linearizability, after  $p_1$  has finished its operation en enqueued element a,  $p_1$  could "call"  $p_2$  and inform it about the availability of "a":  $p_2$  will then be sure to find a. Everything happens as if indeed the enqueue of a was executed at a single point in time.

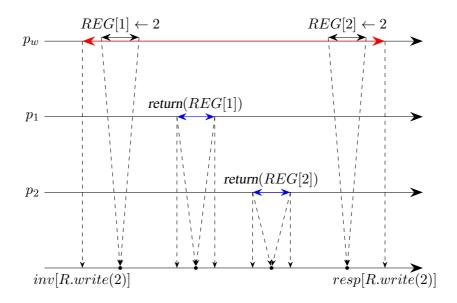

Clearly, any linearizable history is also sequentially consistent. The contrary is not true. A major drawback of sequential consistency is that it is not compositional. To illustrate this, consider the counter-example described in Figure 2.13. The history H depicted in the picture involves two processes  $p_1$  and  $p_2$  accessing two shared registers  $R_1$  and  $R_2$ . It is easy to see that the restriction H to each of the registers is sequentially consistent. Indeed, concerning register  $R_1$ , we can re-order the read of  $p_1$  before the write of  $p_2$  to obtain a sequential history that respects the semantics of a register (initialized to 0). This is possible because the resuting sequential history does not need to respect the real-time ordering of the operations in the original history. Note that the history restricted to  $R_1$  is not linearizable. As for register  $R_2$ , we simply need to order the read of  $p_1$  after the write of  $p_2$ .

Nevertheless, the system composed of the two registers  $R_1$  and  $R_2$  is not sequentially consistent. In every legal equivalent to H, the write on  $R_2$  performed by  $p_2$  should precede the read of  $R_2$  performed by  $p_1$ :  $p_1$  reads the value written by  $p_2$ . If we also want to respect the process-order relation of H on  $p_1$  and  $p_2$ , we obtain the following sequential history:  $p_2.Write_{R_1}(1)$ ;  $p_2.Write_{R_2}(1)$ ;  $p_1.Read_{R_2}(1)$ ;  $p_1.Read_{R_2}(1)$ ;  $p_1.Read_{R_2}(1)$ ;  $p_1.Read_{R_2}(1)$ ;  $p_1.Read_{R_2}(1)$ ;  $p_1.Read_{R_2}(1)$ ;  $p_2.Read_{R_2}(1)$ ;  $p_2.Read_{R_2}(1)$ ;  $p_3.Read_{R_2}(1)$ ;  $p_3.Read_{R$

Figure 2.13.: Sequential consistency is not compositional

# 2.5. Safety

It is convenient to reason about the correctness of a shared object implementation by splitting its properties into *safety* and *liveness*. Intuitively, safety properties ensure that nothing "bad" is ever going to happen whilst liveness properties guarantee that something "good" eventually happens.

More specifically, a *property* is a set of (finite or infinite) histories. Now a property P is a safety property if:

- P is prefix-closed: if  $H \in P$ , then for every prefix H' of  $H, H' \in P$ .

- P is *limit-closed*: for every infinite sequence  $H_0, H_1, \ldots$  of histories, where each  $H_i$  is a prefix of  $H_{i+1}$  and each  $H_i \in P$ , the limit history  $H = \lim_{i \to \infty} H_i$  is in P.

Knowing that a property is a safety one helps prove it in the following sense. To ensure that a safety property P holds for a given implementation, it is enough to show that every *finite* history is in P: a history is in P if and only if each of its *finite* prefixes is in P. Indeed, every infinite history of an implementation is the limit of some sequence of ever-extending finite histories and thus should also be in P.

**Theorem 3** Linearizability is a safety property.

The proof of Theorem 3 uses a slight generalization of König's infinity lemma formulated as follows:

**Lemma 1** (König's Lemma) Let G be an infinite directed graph such that (1) each node of G has finite outdegree, (2) each vertex of G is reachable from some root vertex of G (a vertex with zero indegree), and (3) G has only finitely many roots. Then G has an infinite path with no repeated nodes starting from some root.

Now we prove Theorem 3, i.e., we show that the set of linearizable histories is prefix- and limit-closed. Recall that we only consider objects with finite non-determinism: an operation applied to a given object state may return only finitely many responses and cause only a finite number of state transitions.

**Proof** Consider a linearizable history H. Since linearizability is compositional, we can simply assume that H is a history of operations on a single (composed) object X. We show first that any H', a prefix of H, is also linearizable (with respect to X).

Let S be any linearization of H, i.e., a sequential legal history that is equivalent to (a completion of H) and respects the real-time order of H. Now we construct a sequential history S' as follows: we take the shortest prefix of S that contains all complete operations of H'. Since S contains all compete operations of H', such a prefix of S exists.

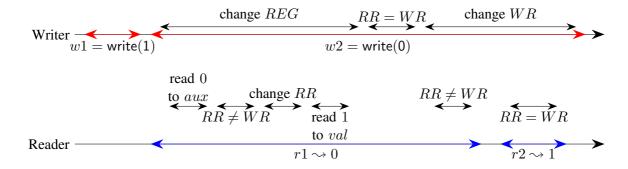

We claim that S' is a linearization of H'. Indeed, let us complete H' by removing operations that do not appear in S' and adding responses to incomplete operations in H' that are present in S'. This way only incomplete operations are removed from H' since, by construction, all operations that are complete in H' appear in S'. Let  $\bar{H}'$  denote the resulting complete history.